Electronics and Communication Engineering - Digital Electronics

Exercise : Digital Electronics - Section 1

- Digital Electronics - Section 13

- Digital Electronics - Section 24

- Digital Electronics - Section 23

- Digital Electronics - Section 22

- Digital Electronics - Section 21

- Digital Electronics - Section 20

- Digital Electronics - Section 19

- Digital Electronics - Section 18

- Digital Electronics - Section 17

- Digital Electronics - Section 16

- Digital Electronics - Section 15

- Digital Electronics - Section 14

- Digital Electronics - Section 1

- Digital Electronics - Section 12

- Digital Electronics - Section 11

- Digital Electronics - Section 10

- Digital Electronics - Section 9

- Digital Electronics - Section 8

- Digital Electronics - Section 7

- Digital Electronics - Section 6

- Digital Electronics - Section 5

- Digital Electronics - Section 4

- Digital Electronics - Section 3

- Digital Electronics - Section 2

31.

Minimum number of 2-input NAND gates required to implement the function F = (x + y) (Z + W) is

Answer: Option

Explanation:

F = (x + y) (z + w) = xy.(z + w)

= xyz + xyw

=  minimum no. of 2 input NAND gate.

minimum no. of 2 input NAND gate.

32.

Which device has one input and many outputs?

Answer: Option

Explanation:

Demultiplexer takes data from one line and directs it to any of its N output depending on the status of its select lines.

33.

A carry look ahead adder is frequently used for addition because

Answer: Option

Explanation:

In look ahead carry adder the carry is directly derived from the gates when original inputs are being added. Hence the addition is fast. This process requires more gates and is costly.

34.

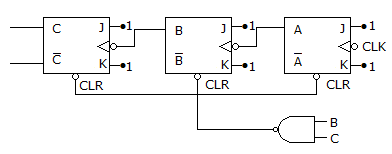

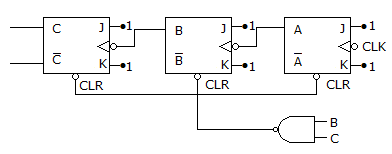

The counter in the given figure is

Answer: Option

Explanation:

When counter is 110 the counter resets. Hence mod 6.

35.

In register index addressing mode the effective address is given by

Answer: Option

Explanation:

4 = 22, in up scaling digit will be shifted by two bit in right direction.

Quick links

Quantitative Aptitude

Verbal (English)

Reasoning

Programming

Interview

Placement Papers