Electronics and Communication Engineering - Digital Electronics

Exercise : Digital Electronics - Section 14

- Digital Electronics - Section 13

- Digital Electronics - Section 24

- Digital Electronics - Section 23

- Digital Electronics - Section 22

- Digital Electronics - Section 21

- Digital Electronics - Section 20

- Digital Electronics - Section 19

- Digital Electronics - Section 18

- Digital Electronics - Section 17

- Digital Electronics - Section 16

- Digital Electronics - Section 15

- Digital Electronics - Section 14

- Digital Electronics - Section 1

- Digital Electronics - Section 12

- Digital Electronics - Section 11

- Digital Electronics - Section 10

- Digital Electronics - Section 9

- Digital Electronics - Section 8

- Digital Electronics - Section 7

- Digital Electronics - Section 6

- Digital Electronics - Section 5

- Digital Electronics - Section 4

- Digital Electronics - Section 3

- Digital Electronics - Section 2

1.

A voltage DAC is generally slower than current DAC

2.

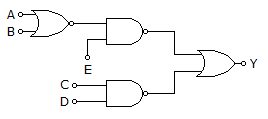

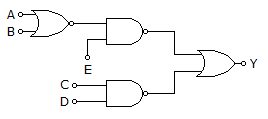

The circuit realizes the function

3.

For a NAND SR latch of input is the normal resting state of inputs is

4.

A mod-2 counter followed by a mod 5 is same as

5.

The write cycle time of memory is 200 nsec. The maximum rate of data which can be stored is

Quick links

Quantitative Aptitude

Verbal (English)

Reasoning

Programming

Interview

Placement Papers