Electronics and Communication Engineering - Digital Electronics

Exercise : Digital Electronics - Section 15

- Digital Electronics - Section 13

- Digital Electronics - Section 24

- Digital Electronics - Section 23

- Digital Electronics - Section 22

- Digital Electronics - Section 21

- Digital Electronics - Section 20

- Digital Electronics - Section 19

- Digital Electronics - Section 18

- Digital Electronics - Section 17

- Digital Electronics - Section 16

- Digital Electronics - Section 15

- Digital Electronics - Section 14

- Digital Electronics - Section 1

- Digital Electronics - Section 12

- Digital Electronics - Section 11

- Digital Electronics - Section 10

- Digital Electronics - Section 9

- Digital Electronics - Section 8

- Digital Electronics - Section 7

- Digital Electronics - Section 6

- Digital Electronics - Section 5

- Digital Electronics - Section 4

- Digital Electronics - Section 3

- Digital Electronics - Section 2

16.

The fetching, decoding and executing of an instruction is broken down into several time intervals. Each of these intervals, involving one or more clock periods, is called a

17.

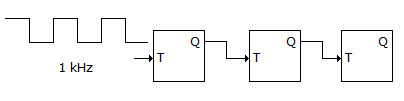

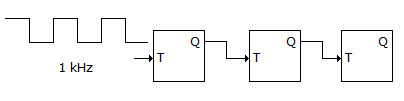

The output of the circuit shown below will be of the frequency

18.

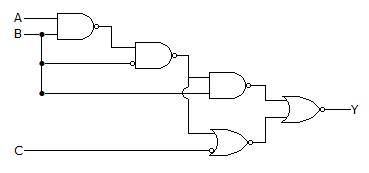

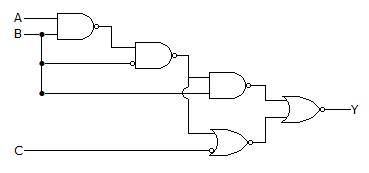

In the given figure Y =

19.

Assertion (A): An encoder converts key dips to binary code.

Reason (R): An encoder has more inputs than output.

20.

If a RAM has 34 bits in its MAR and 16 bits in its MDR, then its capacity will be

Quick links

Quantitative Aptitude

Verbal (English)

Reasoning

Programming

Interview

Placement Papers