Electronics and Communication Engineering - Digital Electronics

Exercise : Digital Electronics - Section 6

- Digital Electronics - Section 13

- Digital Electronics - Section 24

- Digital Electronics - Section 23

- Digital Electronics - Section 22

- Digital Electronics - Section 21

- Digital Electronics - Section 20

- Digital Electronics - Section 19

- Digital Electronics - Section 18

- Digital Electronics - Section 17

- Digital Electronics - Section 16

- Digital Electronics - Section 15

- Digital Electronics - Section 14

- Digital Electronics - Section 1

- Digital Electronics - Section 12

- Digital Electronics - Section 11

- Digital Electronics - Section 10

- Digital Electronics - Section 9

- Digital Electronics - Section 8

- Digital Electronics - Section 7

- Digital Electronics - Section 6

- Digital Electronics - Section 5

- Digital Electronics - Section 4

- Digital Electronics - Section 3

- Digital Electronics - Section 2

46.

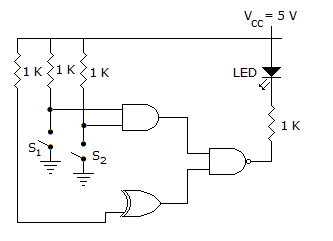

In the figure, the LED

Answer: Option

Explanation:

To emit the light, it is necessary NAND gate output is zero, for NAND O/P zero. Both the I/O must be height. And it is not possible in any case.

47.

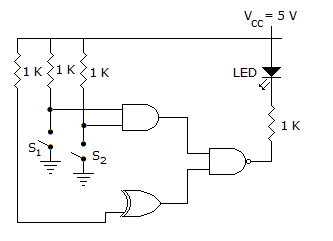

A 4 bit ripple counter uses flip flops with propagation delay of 50 ns each. The maximum clock frequency which can be used is

Answer: Option

Explanation:

Time delay = 50 x 4 x 10-9s,

.

.

48.

An AND gate has two inputs A and B and one inhibit input S. Out of total 8 input states, output is 1 in

Answer: Option

Explanation:

Only one input, i.e., A = 1, B = 1 and S = 0 gives output 1.

49.

26810 = __________ .

Answer: Option

Explanation:

10C in hexadecimal = 1 x 162 + 12 = 268 in decimal.

50.

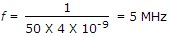

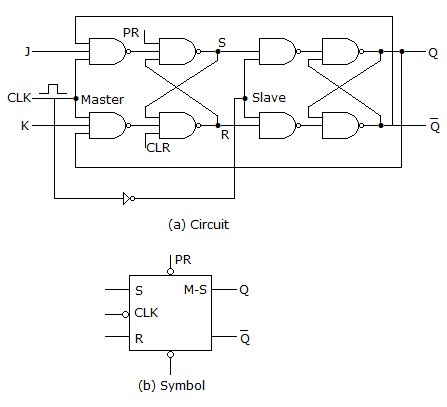

In a JK Master slave flip flop

Answer: Option

Explanation:

Quick links

Quantitative Aptitude

Verbal (English)

Reasoning

Programming

Interview

Placement Papers