Electronics and Communication Engineering - Digital Electronics

Exercise : Digital Electronics - Section 3

- Digital Electronics - Section 13

- Digital Electronics - Section 24

- Digital Electronics - Section 23

- Digital Electronics - Section 22

- Digital Electronics - Section 21

- Digital Electronics - Section 20

- Digital Electronics - Section 19

- Digital Electronics - Section 18

- Digital Electronics - Section 17

- Digital Electronics - Section 16

- Digital Electronics - Section 15

- Digital Electronics - Section 14

- Digital Electronics - Section 1

- Digital Electronics - Section 12

- Digital Electronics - Section 11

- Digital Electronics - Section 10

- Digital Electronics - Section 9

- Digital Electronics - Section 8

- Digital Electronics - Section 7

- Digital Electronics - Section 6

- Digital Electronics - Section 5

- Digital Electronics - Section 4

- Digital Electronics - Section 3

- Digital Electronics - Section 2

16.

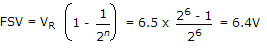

Find the FSV (full scale voltage) in a 6 bit R-2R ladder D/A converter has a reference voltage of 6.5 V.

Answer: Option

Explanation:

.

.

17.

Parallel adder is

Answer: Option

Explanation:

Adder is a combinational circuit.

18.

An 8 bit binary number is to be entered into an 8 bit serial shift register. The number of clock pulses required is

Answer: Option

Explanation:

In serial shift register one pulse is needed to store each bit.

19.

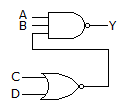

In the given figure, A = B = 1 and C = D = 0. Then Y =

Answer: Option

Explanation:

The CD inputs when fed to NOR gate give output 1. Therefore Y = 1.1.1 = 0.

20.

Assertion (A): CMOS devices have very high speed.

Reason (R): CMOS devices have very small physical size and simple geometry.

Answer: Option

Explanation:

CMOS has high packing density but low speed.

Quick links

Quantitative Aptitude

Verbal (English)

Reasoning

Programming

Interview

Placement Papers