Electronics and Communication Engineering - Digital Electronics

Exercise : Digital Electronics - Section 2

- Digital Electronics - Section 13

- Digital Electronics - Section 24

- Digital Electronics - Section 23

- Digital Electronics - Section 22

- Digital Electronics - Section 21

- Digital Electronics - Section 20

- Digital Electronics - Section 19

- Digital Electronics - Section 18

- Digital Electronics - Section 17

- Digital Electronics - Section 16

- Digital Electronics - Section 15

- Digital Electronics - Section 14

- Digital Electronics - Section 1

- Digital Electronics - Section 12

- Digital Electronics - Section 11

- Digital Electronics - Section 10

- Digital Electronics - Section 9

- Digital Electronics - Section 8

- Digital Electronics - Section 7

- Digital Electronics - Section 6

- Digital Electronics - Section 5

- Digital Electronics - Section 4

- Digital Electronics - Section 3

- Digital Electronics - Section 2

21.

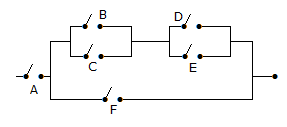

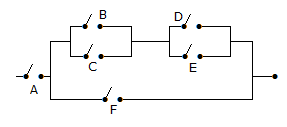

The Boolean expression for the circuit of the given figure

Answer: Option

Explanation:

B and C in parallel give B + C. Similarly D and E in parallel give D + E. (B + C) in series with (D + E) give (B + C) (D + E). Since F is in parallel we get F + (B + C) (D + E). Finally A is in series. Therefore we get A[F + (B + C) (D + E)].

22.

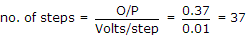

What will be BCD number when the output is 0.37 V?

Answer: Option

Explanation:

BCD number is (00110111).

23.

The first machine cycle of an instruction is always

Answer: Option

Explanation:

Fetch cycle is always first machine cycle.

24.

A counter has N flip flops. The total number of states are

Answer: Option

Explanation:

One flip-flop means 2 states and N flip-flops means 2N states.

25.

Out of S, R, J, K, Preset, Clear inputs to flip flops, the synchronous inputs are

Answer: Option

Explanation:

Preset and clear inputs are not applied in any fixed sequence.

Quick links

Quantitative Aptitude

Verbal (English)

Reasoning

Programming

Interview

Placement Papers