Digital Electronics - Flip-Flops

Exercise : Flip-Flops - General Questions

- Flip-Flops - General Questions

- Flip-Flops - True or False

- Flip-Flops - Filling the Blanks

71.

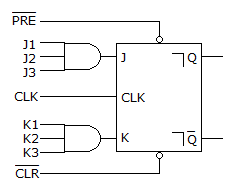

The circuit given below fails to function; the inputs are checked with a logic probe and the following indications are obtained: CLK, J1, J2, J3, K1, K2, and K3 are pulsing. Q and  are HIGH.

are HIGH.  and PRE are LOW. What could be causing the problem?

and PRE are LOW. What could be causing the problem?

72.

A push-button switch is used to input data to a register. The output of the register is erratic. What could be causing the problem?

73.

A 555 timer is connected for astable operation as shown below along with the output waveform. It is determined that the duty cycle should be 0.5. What steps need to be taken to correct the duty cycle, while maintaining the same output frequency?

74.

The pulse width of a one-shot circuit is determined by ________.

75.

For an S-R flip-flop to be set or reset, the respective input must be:

Quick links

Quantitative Aptitude

Verbal (English)

Reasoning

Programming

Interview

Placement Papers