Digital Electronics - Flip-Flops

Exercise : Flip-Flops - General Questions

- Flip-Flops - General Questions

- Flip-Flops - True or False

- Flip-Flops - Filling the Blanks

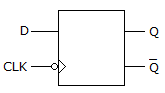

36.

The symbols on this flip-flop device indicate ________.

37.

In a 555 timer, three 5 k resistors provide a trigger level of ________.

resistors provide a trigger level of ________.

resistors provide a trigger level of ________.

resistors provide a trigger level of ________.38.

Does the cross-coupled NOR flip-flop have active-HIGH or active-LOW set and reset inputs?

39.

The circuit that is primarily responsible for certain flip-flops to be designated as edge-triggered is the:

40.

With four J-K flip-flops wired as an asynchronous counter, the first output change of divider #4 indicates a count of how many input clock pulses?

Quick links

Quantitative Aptitude

Verbal (English)

Reasoning

Programming

Interview

Placement Papers