Electronics and Communication Engineering - Exam Questions Papers

Exercise : Exam Questions Papers - Exam Paper 16

- Exam Questions Papers - Exam Paper 12

- Exam Questions Papers - Exam Paper 22

- Exam Questions Papers - Exam Paper 21

- Exam Questions Papers - Exam Paper 20

- Exam Questions Papers - Exam Paper 19

- Exam Questions Papers - Exam Paper 18

- Exam Questions Papers - Exam Paper 17

- Exam Questions Papers - Exam Paper 16

- Exam Questions Papers - Exam Paper 15

- Exam Questions Papers - Exam Paper 14

- Exam Questions Papers - Exam Paper 13

- Exam Questions Papers - Exam Paper 1

- Exam Questions Papers - Exam Paper 11

- Exam Questions Papers - Exam Paper 10

- Exam Questions Papers - Exam Paper 9

- Exam Questions Papers - Exam Paper 8

- Exam Questions Papers - Exam Paper 7

- Exam Questions Papers - Exam Paper 6

- Exam Questions Papers - Exam Paper 5

- Exam Questions Papers - Exam Paper 4

- Exam Questions Papers - Exam Paper 3

- Exam Questions Papers - Exam Paper 2

46.

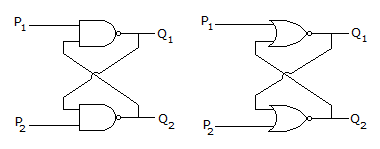

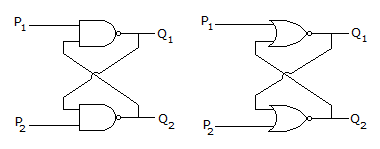

Refer to the NAND and NOR latches shown in the figure. The inputs (P1, P2) for both the latches are first made (0, 1) and then, after a few seconds, made (1, 1). The corresponding stable outputs (Q1, Q2) are

47.

Consider the following two statements about the internal conditions in an n-channel MOSFET operating in the active region

S1: The inversion charge decreases from source to drain

S2: The channel potential increases from source to drain

Which of the following is correct?

S1: The inversion charge decreases from source to drain

S2: The channel potential increases from source to drain

Which of the following is correct?

48.

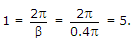

The wavelength of a wave with propagation constant (0.1p + j0.4p)m-1 is

Answer: Option

Explanation:

γ = a + jβ

∴ β = 0.4p

49.

For what positive value of K does the polynomial s4 + 8s3 + 24s2 + 32s + K have roots with zero real parts?

50.

Which of the following capabilities are available in a Universal Shift Register?

- Shift left

- Shift right

- Parallel load

- Serial add

Quick links

Quantitative Aptitude

Verbal (English)

Reasoning

Programming

Interview

Placement Papers