Electronics and Communication Engineering - Networks Analysis and Synthesis

Exercise : Networks Analysis and Synthesis - Section 17

- Networks Analysis and Synthesis - Section 14

- Networks Analysis and Synthesis - Section 27

- Networks Analysis and Synthesis - Section 26

- Networks Analysis and Synthesis - Section 25

- Networks Analysis and Synthesis - Section 24

- Networks Analysis and Synthesis - Section 23

- Networks Analysis and Synthesis - Section 22

- Networks Analysis and Synthesis - Section 21

- Networks Analysis and Synthesis - Section 20

- Networks Analysis and Synthesis - Section 19

- Networks Analysis and Synthesis - Section 18

- Networks Analysis and Synthesis - Section 17

- Networks Analysis and Synthesis - Section 16

- Networks Analysis and Synthesis - Section 15

- Networks Analysis and Synthesis - Section 1

- Networks Analysis and Synthesis - Section 13

- Networks Analysis and Synthesis - Section 12

- Networks Analysis and Synthesis - Section 11

- Networks Analysis and Synthesis - Section 10

- Networks Analysis and Synthesis - Section 9

- Networks Analysis and Synthesis - Section 8

- Networks Analysis and Synthesis - Section 7

- Networks Analysis and Synthesis - Section 6

- Networks Analysis and Synthesis - Section 5

- Networks Analysis and Synthesis - Section 4

- Networks Analysis and Synthesis - Section 3

- Networks Analysis and Synthesis - Section 2

36.

A series resonant circuit is capacitive at f = 150 Hz. The circuit will be inductive somewhere at

37.

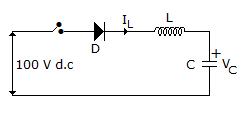

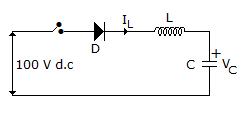

In the circuit of figure, the switch is closed at t = 0 with iL (0) = 0 and VC (0) = 0. In the steady state nc equals.

38.

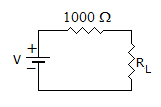

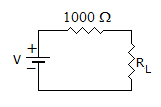

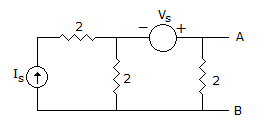

The maximum power that can be transferred to the load is resistor RL from the voltage source in the figure is

39.

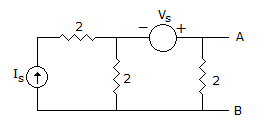

The Thevenin equivalent circuit to the left of AB has Req

40.

A current increasing at the rate of 1A/s is passed through a 1 H inductor. At t = 0, i = 0. The flux linkages after 1 sec are

Quick links

Quantitative Aptitude

Verbal (English)

Reasoning

Programming

Interview

Placement Papers