Digital Electronics - Logic Gates

Exercise : Logic Gates - Filling the Blanks

- Logic Gates - General Questions

- Logic Gates - True or False

- Logic Gates - Filling the Blanks

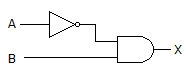

1.

The gates in this figure are implemented using TTL logic. If the input of the inverter is open, and you apply logic pulses to point B, the output of the AND gate will be ________.

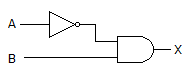

2.

The gates in this figure are implemented using TTL logic. If the output of the inverter is open, and you apply logic pulses to point B, the output of the AND gate will be ________.

3.

If A is LOW or B is LOW or BOTH are LOW, then X is LOW. If A is HIGH and B is HIGH, then X is HIGH. These rules specify the operation of a(n) ________.

4.

A major advantage of ECL logic over TTL and CMOS is ________.

5.

The output of an XOR gate is HIGH only when ________.

Quick links

Quantitative Aptitude

Verbal (English)

Reasoning

Programming

Interview

Placement Papers