Electronics and Communication Engineering - Networks Analysis and Synthesis

Exercise : Networks Analysis and Synthesis - Section 20

- Networks Analysis and Synthesis - Section 14

- Networks Analysis and Synthesis - Section 27

- Networks Analysis and Synthesis - Section 26

- Networks Analysis and Synthesis - Section 25

- Networks Analysis and Synthesis - Section 24

- Networks Analysis and Synthesis - Section 23

- Networks Analysis and Synthesis - Section 22

- Networks Analysis and Synthesis - Section 21

- Networks Analysis and Synthesis - Section 20

- Networks Analysis and Synthesis - Section 19

- Networks Analysis and Synthesis - Section 18

- Networks Analysis and Synthesis - Section 17

- Networks Analysis and Synthesis - Section 16

- Networks Analysis and Synthesis - Section 15

- Networks Analysis and Synthesis - Section 1

- Networks Analysis and Synthesis - Section 13

- Networks Analysis and Synthesis - Section 12

- Networks Analysis and Synthesis - Section 11

- Networks Analysis and Synthesis - Section 10

- Networks Analysis and Synthesis - Section 9

- Networks Analysis and Synthesis - Section 8

- Networks Analysis and Synthesis - Section 7

- Networks Analysis and Synthesis - Section 6

- Networks Analysis and Synthesis - Section 5

- Networks Analysis and Synthesis - Section 4

- Networks Analysis and Synthesis - Section 3

- Networks Analysis and Synthesis - Section 2

31.

Assertion (A): When capacitor is fed by a dc voltage given a capacitor behaves as short circuit at t = 0 and open circuit at f = ∞.

Reason (R): The impedance of a capacitor is

32.

- P(s) = s4 + s3 + 2s2 + 4s + 3

- Q(s) = s4 + 2s3 + s

33.

The material used for fuse must have

34.

The function δ (t - b) is a

35.

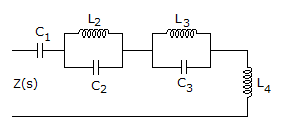

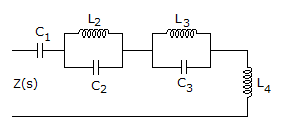

The circuit in figure is

Quick links

Quantitative Aptitude

Verbal (English)

Reasoning

Programming

Interview

Placement Papers