Electronics and Communication Engineering - Networks Analysis and Synthesis

Exercise : Networks Analysis and Synthesis - Section 18

- Networks Analysis and Synthesis - Section 14

- Networks Analysis and Synthesis - Section 27

- Networks Analysis and Synthesis - Section 26

- Networks Analysis and Synthesis - Section 25

- Networks Analysis and Synthesis - Section 24

- Networks Analysis and Synthesis - Section 23

- Networks Analysis and Synthesis - Section 22

- Networks Analysis and Synthesis - Section 21

- Networks Analysis and Synthesis - Section 20

- Networks Analysis and Synthesis - Section 19

- Networks Analysis and Synthesis - Section 18

- Networks Analysis and Synthesis - Section 17

- Networks Analysis and Synthesis - Section 16

- Networks Analysis and Synthesis - Section 15

- Networks Analysis and Synthesis - Section 1

- Networks Analysis and Synthesis - Section 13

- Networks Analysis and Synthesis - Section 12

- Networks Analysis and Synthesis - Section 11

- Networks Analysis and Synthesis - Section 10

- Networks Analysis and Synthesis - Section 9

- Networks Analysis and Synthesis - Section 8

- Networks Analysis and Synthesis - Section 7

- Networks Analysis and Synthesis - Section 6

- Networks Analysis and Synthesis - Section 5

- Networks Analysis and Synthesis - Section 4

- Networks Analysis and Synthesis - Section 3

- Networks Analysis and Synthesis - Section 2

41.

The sum of positive real function is positive real.

42.

Assertion (A): KCL is dual of KVL.

Reason (R): Node is dual of mesh.

43.

For a 2 port network, the O/P short circuit current was measured with a 1 volt source at the I/P then value of the current gives

44.

The time constant of the capacitance circuit is defined as the time during which voltage

45.

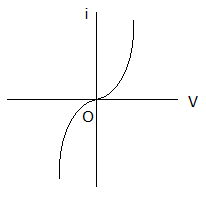

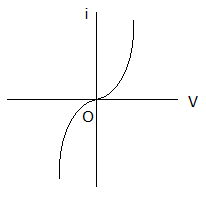

Figure shows the V-i characteristics of a material. The material is likely to be

Quick links

Quantitative Aptitude

Verbal (English)

Reasoning

Programming

Interview

Placement Papers