Electronics and Communication Engineering - Networks Analysis and Synthesis

Exercise : Networks Analysis and Synthesis - Section 18

- Networks Analysis and Synthesis - Section 14

- Networks Analysis and Synthesis - Section 27

- Networks Analysis and Synthesis - Section 26

- Networks Analysis and Synthesis - Section 25

- Networks Analysis and Synthesis - Section 24

- Networks Analysis and Synthesis - Section 23

- Networks Analysis and Synthesis - Section 22

- Networks Analysis and Synthesis - Section 21

- Networks Analysis and Synthesis - Section 20

- Networks Analysis and Synthesis - Section 19

- Networks Analysis and Synthesis - Section 18

- Networks Analysis and Synthesis - Section 17

- Networks Analysis and Synthesis - Section 16

- Networks Analysis and Synthesis - Section 15

- Networks Analysis and Synthesis - Section 1

- Networks Analysis and Synthesis - Section 13

- Networks Analysis and Synthesis - Section 12

- Networks Analysis and Synthesis - Section 11

- Networks Analysis and Synthesis - Section 10

- Networks Analysis and Synthesis - Section 9

- Networks Analysis and Synthesis - Section 8

- Networks Analysis and Synthesis - Section 7

- Networks Analysis and Synthesis - Section 6

- Networks Analysis and Synthesis - Section 5

- Networks Analysis and Synthesis - Section 4

- Networks Analysis and Synthesis - Section 3

- Networks Analysis and Synthesis - Section 2

31.

If f(t) = r (t - a), F(s) =

32.

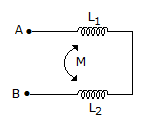

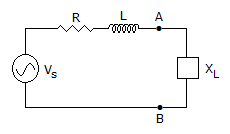

For the network in figure, which of the following expressions gives the value of net inductance between terminals A and B

- L1 ± L2

- L1 ± L2 ± M

- L1 ± L2 - 2M

- L1 ± L2 ± 2M

33.

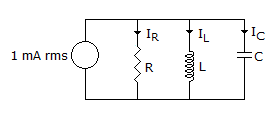

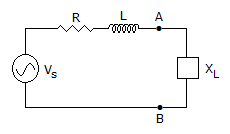

The parallel RLC circuit shown in figure is in resonance. If

34.

An ideal voltage source can not be converted into an equivalent current source.

35.

Load ZL for maximum power transfer is

Quick links

Quantitative Aptitude

Verbal (English)

Reasoning

Programming

Interview

Placement Papers