Electronics and Communication Engineering - Electronic Devices and Circuits

Exercise : Electronic Devices and Circuits - Section 7

- Electronic Devices and Circuits - Section 13

- Electronic Devices and Circuits - Section 24

- Electronic Devices and Circuits - Section 23

- Electronic Devices and Circuits - Section 22

- Electronic Devices and Circuits - Section 21

- Electronic Devices and Circuits - Section 20

- Electronic Devices and Circuits - Section 19

- Electronic Devices and Circuits - Section 18

- Electronic Devices and Circuits - Section 17

- Electronic Devices and Circuits - Section 16

- Electronic Devices and Circuits - Section 15

- Electronic Devices and Circuits - Section 14

- Electronic Devices and Circuits - Section 1

- Electronic Devices and Circuits - Section 12

- Electronic Devices and Circuits - Section 11

- Electronic Devices and Circuits - Section 10

- Electronic Devices and Circuits - Section 9

- Electronic Devices and Circuits - Section 8

- Electronic Devices and Circuits - Section 7

- Electronic Devices and Circuits - Section 6

- Electronic Devices and Circuits - Section 5

- Electronic Devices and Circuits - Section 4

- Electronic Devices and Circuits - Section 3

- Electronic Devices and Circuits - Section 2

26.

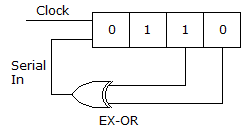

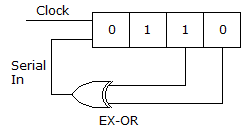

In following figure, the initial contents of the 4-bit serial in parallel out, right shift, shift register as shown in figure are 0110. After 3 clock pulses the contents of the shift register will be

Answer: Option

Explanation:

27.

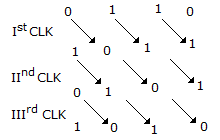

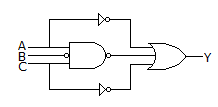

For the logic circuit of the given figure, the minimized expression is

Answer: Option

Explanation:

+ A + C = A + B + C + A + C = A + C + B

+ A + C = A + B + C + A + C = A + C + B

=

28.

Binary multiplication can be done by repeated addition.

29.

Assertion (A): In totem pole output the output impedance is low.

Reason (R): TTL gate with active pull up should not be used in wired AND connection.

30.

A 4 bit synchronous counter uses flip flops with a delay time of 15 ns each. The time required for change of state is

Answer: Option

Explanation:

In a synchronous counter clock input is applied to all flip flops simultaneously. Hence total delay time is 15 ns.

Quick links

Quantitative Aptitude

Verbal (English)

Reasoning

Programming

Interview

Placement Papers