Electronics and Communication Engineering - Electronic Devices and Circuits

Exercise : Electronic Devices and Circuits - Section 6

- Electronic Devices and Circuits - Section 13

- Electronic Devices and Circuits - Section 24

- Electronic Devices and Circuits - Section 23

- Electronic Devices and Circuits - Section 22

- Electronic Devices and Circuits - Section 21

- Electronic Devices and Circuits - Section 20

- Electronic Devices and Circuits - Section 19

- Electronic Devices and Circuits - Section 18

- Electronic Devices and Circuits - Section 17

- Electronic Devices and Circuits - Section 16

- Electronic Devices and Circuits - Section 15

- Electronic Devices and Circuits - Section 14

- Electronic Devices and Circuits - Section 1

- Electronic Devices and Circuits - Section 12

- Electronic Devices and Circuits - Section 11

- Electronic Devices and Circuits - Section 10

- Electronic Devices and Circuits - Section 9

- Electronic Devices and Circuits - Section 8

- Electronic Devices and Circuits - Section 7

- Electronic Devices and Circuits - Section 6

- Electronic Devices and Circuits - Section 5

- Electronic Devices and Circuits - Section 4

- Electronic Devices and Circuits - Section 3

- Electronic Devices and Circuits - Section 2

21.

Assertion (A): Master slave JK flip flop is commonly used in high speed synchronous circuitry

Reason (R): Master slave JK flip flop uses two JK flip flops in cascade.

Answer: Option

Explanation:

R-S, J-K flip-flop is not used very commonly.

22.

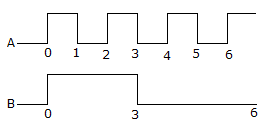

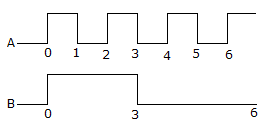

Inputs A and B of the given figure are applied to a NAND gate. The output is LOW

Answer: Option

Explanation:

NAND gate gives Low output if all inputs are High. For other combinations of inputs, output is High.

23.

ECL is a saturating logic.

Answer: Option

Explanation:

It is a non-saturating logic. Hence highest speed of operation.

24.

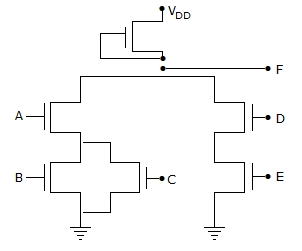

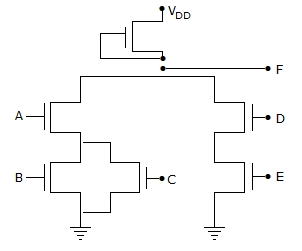

For the NMOS gate in the given figure, F =

Answer: Option

Explanation:

B + C are in parallel and A is in series with this parallel combination, Similarly D + E are in series. Then D, E are in parallel with A, B and C Y = A(B + C) + DE .

25.

The resolution of 4 bit counting ADC is 0.5 volt, for an Analog input of 6.6 volts. The digital output of ADC will be

Answer: Option

Explanation:

Digital output of ADC resolution =  .

.

Quick links

Quantitative Aptitude

Verbal (English)

Reasoning

Programming

Interview

Placement Papers