Electronics and Communication Engineering - Digital Electronics - Discussion

Discussion Forum : Digital Electronics - Section 6 (Q.No. 34)

34.

A 4 bit synchronous counter has flip flops having propagation delay of 50 ns each and AND gates having propagation delay of 20 ns each. The maximum frequency of clock pulses can be

Answer: Option

Explanation:

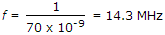

Maximum delay = 50 + 20 = 70 x 10-9 s.

Hence  .

.

Discussion:

2 comments Page 1 of 1.

Pavithran S said:

8 months ago

Yes, @Ska.

There are two AND gates having a delay of 40 ns, so the total delay will be 90 ns.

The answer will be 11.1 MHZ.

There are two AND gates having a delay of 40 ns, so the total delay will be 90 ns.

The answer will be 11.1 MHZ.

Ska said:

6 years ago

shouldn't max delay be ( 50 + 20 + 20 ) ns? Please explain.

Post your comments here:

Quick links

Quantitative Aptitude

Verbal (English)

Reasoning

Programming

Interview

Placement Papers