Digital Electronics - Integrated-Circuit Logic Families

Exercise : Integrated-Circuit Logic Families - General Questions

- Integrated-Circuit Logic Families - General Questions

- Integrated-Circuit Logic Families - True or False

- Integrated-Circuit Logic Families - Filling the Blanks

21.

Whenever a totem-pole TTL output goes from LOW to HIGH, a high-amplitude current spike is drawn from the Vcc supply. How is this effect corrected to a digital circuit?

22.

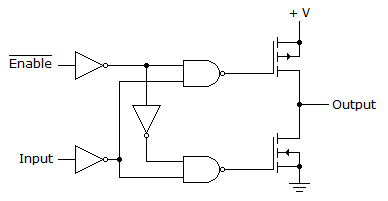

What type of circuit is shown below and which statement best describes its operation?

23.

What is the increase in switching speed between 74LS series TTL and 74HC/HCT (High-Speed CMOS)?

24.

A logic signal experiences a delay in going through a circuit. The two propagation delay times are defined as:

25.

What does ECL stand for?

Quick links

Quantitative Aptitude

Verbal (English)

Reasoning

Programming

Interview

Placement Papers