Digital Electronics - Integrated-Circuit Logic Families

Exercise : Integrated-Circuit Logic Families - General Questions

- Integrated-Circuit Logic Families - General Questions

- Integrated-Circuit Logic Families - True or False

- Integrated-Circuit Logic Families - Filling the Blanks

11.

What must be done to interface CMOS to TTL?

12.

What is the static charge that can be stored by your body as you walk across a carpet?

13.

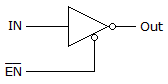

What type of circuit is shown below, and how is the output ordinarily connected?

14.

What type of circuit is represented in the given figure, and which statement best describes its operation?

15.

Which of the following logic families has the highest noise margin?

Quick links

Quantitative Aptitude

Verbal (English)

Reasoning

Programming

Interview

Placement Papers