Digital Electronics - Combinational Logic Circuits - Discussion

Discussion Forum : Combinational Logic Circuits - General Questions (Q.No. 16)

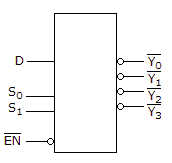

16.

For the device shown here, assume the D input is LOW, both S inputs are HIGH, and the  input is HIGH. What is the status of the

input is HIGH. What is the status of the  outputs?

outputs?

Discussion:

10 comments Page 1 of 1.

Alex said:

1 year ago

Both S inputs are HIGH, which means output is reflected at y3.

Samaina said:

7 years ago

Yes, you are right @Shreashi.

Rachit said:

9 years ago

This is a demultiplexer. When S0 and S1 are both 0, output would be D000. That implies 0000, but since we have inverters present at the outputs the answer gets inverted and we get 1111.

(1)

Shreashi said:

9 years ago

EN' input is high. But since it is complement it will be low. And since all the outputs are in complemented form low input will become high. So Y' is high.

(1)

Surya said:

9 years ago

If enable input is high then it is not enabled. And how we tell output is high?

(2)

Dhana said:

1 decade ago

For a given MUX, EN i/p is active low i.e, MUX is active if and only if EN=0, but they given EN=1, so MUX is in disable condition.

The resultant o/p is all zeros. But o/p is inverted, so o/p is all ones.

The resultant o/p is all zeros. But o/p is inverted, so o/p is all ones.

(2)

Rupesh9292 said:

1 decade ago

Still didn't get it clearly please elaborate. En=1 o/p=1. It's all o/p=1 en=0 o/p=0 means all o/p=0 how came? If o/p condition is 1010 then what is i/p?

Hiren said:

1 decade ago

Answer is High because, Output of Demax is Inverted.

So when Output cames 0 it gets inverted So. Ultimately It is all High is answer.

So when Output cames 0 it gets inverted So. Ultimately It is all High is answer.

Prakul said:

1 decade ago

High impedence because we are providing HIGH to EN input. EN pin is active low enable pin. If we set it as HIGH, the outputs will be in high impedence state.

(1)

Samir said:

1 decade ago

High impedance.

Post your comments here:

Quick links

Quantitative Aptitude

Verbal (English)

Reasoning

Programming

Interview

Placement Papers

are LOW.

are LOW. are HIGH.

are HIGH.