Digital Electronics - Combinational Logic Analysis

Exercise : Combinational Logic Analysis - Filling the Blanks

- Combinational Logic Analysis - General Questions

- Combinational Logic Analysis - True or False

- Combinational Logic Analysis - Filling the Blanks

1.

Assume you have A, B, C, and D available but not their complements. The minimum number of 2-input NAND gates required to implement the equation  is ________.

is ________.

is ________.

is ________.2.

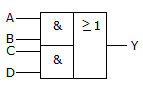

The symbol shown represents a(n) ________.

3.

A gate can drive a number of load gate inputs up to its specified ________.

4.

The expression  can be directly implemented using only ________.

can be directly implemented using only ________.

can be directly implemented using only ________.

can be directly implemented using only ________.5.

The symbol shown represents ________.

Quick links

Quantitative Aptitude

Verbal (English)

Reasoning

Programming

Interview

Placement Papers