Digital Electronics - Counters

Exercise : Counters - Filling the Blanks

- Counters - General Questions

- Counters - True or False

- Counters - Filling the Blanks

11.

A(n) ________ one-shot starts a pulse in response to a trigger and will restart the internal pulse timer every time a subsequent trigger edge occurs before the pulse is complete.

12.

Assume you want to determine the timing diagram for a 4-bit counter using an oscilloscope. The best choice for an oscilloscope trigger signal is ________.

13.

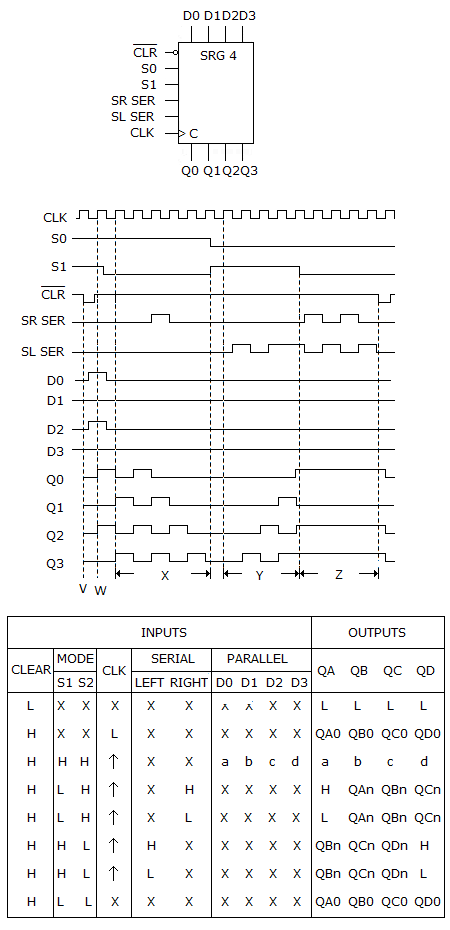

Referring to the function table given below, taking the CLEAR, S1, and S0 inputs all HIGH ________.

14.

Assume a 4-bit ripple counter has a failure in the second flip-flop such that it "locks up." The third and fourth stages will ________.

15.

In order to use a shift register as a counter, ________.

Quick links

Quantitative Aptitude

Verbal (English)

Reasoning

Programming

Interview

Placement Papers